Using PLL Divisors and Timers to Achieve Non-standard Frequencies

3/15/20The Easy Version

If you want to use PWM to generate a particular frequency, it is not too difficult to count out the number of clock cycles you need to create this frequency. That is, assuming it is an integer divisor of your bus frequency. I would also add that it should be an even divisor, since to acheive a 50% duty cycle, the divisor will have to be cut in half.

To do this, we need to find two integer values to put in our PWM counter match registers, one to mark the total length of the period, and one to create the half cycle low or high. Let's assume we'll need close to 50%, and the goal here is output of a specific user defined frequency, so we won't worry about the "even" part. To find the period in clock cycles, we simply divide the bus frequency by the desired frequency:

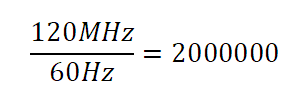

For example, let's say we want a 60Hz PWM, and our bus frequency is 120MHz. We need to set the counter period to 2,000,000 cycles. Easy to do, assuming you are not using a 16 bit counter.

uint32_t Uint32ToStr(char* buff, size_t digits, uint32_t num)

{

/*stuff here*/

}